## Void Shape Evolution of Silicon: Level-Set Approach

C. Grau Turuelo<sup>1</sup>, C. Breitkopf<sup>1</sup>

<sup>1</sup>Technische Universität Dresden, Dresden, Germany

## Abstract

The void shape evolution of silicon is a process driven mainly by surface diffusion which leads to a geometrical transformation of trenches etched in silicon wafers due to surface energy minimization. The final transformation depends on the initial arrangement of the trenches and how close they are from each other. The temperature, the ambient gas and the annealing time affect the velocity of the process as well [1-4]. Most applications are oriented to the creation of an insulating cavity for building electronic devices over it. They are called SON-devices (Silicon-On-Nothing) and they are similar to those SOI (Silicon-On-Insulator) ones [5-6]. The unique special characteristic of this process is the creation of such cavities with no additional etching processes.

The study was initially proposed with the Moving Mesh (ALE) method because of the surface nature of the process. However, some limitations were found (no possibility of coalescence) and the study has been continued with the Level-Set Method. The level set variable serves as the variable which tracks the interface and give the information about how the surface changes with the time (curvature). Afterwards, the output from this variable is used with some custom PDEs to resemble the surface diffusion equation and get the velocity of the interface with the aid of a self-built curvature function. This velocity is then used as the convection velocity in the Level-Set module.

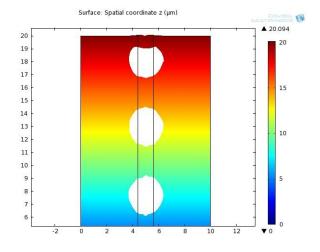

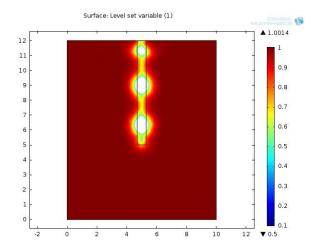

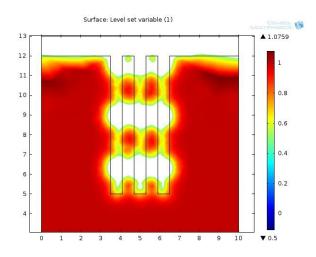

The Level-Set method provides a better output of the final geometries that are unveiled at the end of the simulation. Furthermore, the coalescence of two voids can be simulated in this way. In Figure 1, the old method with Moving Mesh is shown [7-8]. In Figure 2, the Level set method is shown with a big increase in the resolution, in addition to the use of lower mesh element sizes and a smoother movement. In Figure 3, the coalescence has been successfully calculated. This enhances the study and prediction of empty space structures formed with the void shape evolution.

The use of custom PDEs in COMSOL Multiphysics® and the Level-Set method provide a good base platform for the analysis of time dependent structures which are not possible to follow in an actual experiment. This opens a way to optimize the process (temperature and pressure) when a desired geometry must be achieved. It is also possible to simulate the coalescence of several voids with fairly high volume conservation. Thus, it helps to the prediction of the void shape evolution depending on different conditions which improves the controllability and the feasibility of building new micro-electronic or micro-electromechanical devices such as pressure sensors,

transistors or optical devices [9].

## Reference

1. I. Mizushima et al., "Empty-space-in-silicon technique for fabricating a silicon-on-nothing structure", Appl. Phys. Lett. 77, 3290 (2000).

2. T. Sato et al., "Fabrication of Silicon-on-Nothing Structure by Substrate Engineering Using the Empty-Space-in-Silicon Fomation Technique", Jpn. J. Appl. Phys. 43, 12 (2004).

3. K. Sudoh et al., "Numerical Study on Shape Transformation of Silicon Trenches by High-Temperature Hydrogen Annealing", Jpn. J. Appl. Phys. 43, 5937 (2004).

4. K. Sudoh et al., "Void shape evolution and formation of silicon-on-nothing structures during hydrogen annealing of hole arrays on Si(001)", J. Appl. Phys. 105, 083536 (2009).

5. M. Jurczak et al., "Silicon-on-Nothing (SON) - an Innovative Process for Advanced CMOS", IEEE Trans. Electron Devices 47, 2179 (2000).

6. S. Monfray et al., "First 80nm SON (Silicon-On-Nothing) MOSFETs with perfect morphology and high electrical performance", in 2001 International Electron Devices Meeting, Washington DC, United States, 2 December–5 December 2001, pp. 645-648.

7. C. Grau Turuelo et al., "Theoretical Simulations of Silicon-On-Nothing (SON) Structures", Proceedings of the COMSOL Conference Europe Milan 2012 (10-12 October 2012).

8. C. Grau Turuelo, "Void Shape Evolution of Silicon Simulation in COMSOL Multiphysics®", Proceedings of the COMSOL Conference Europe Rotterdam 2013 (23-25 October 2013).

9. T. Sato et al., "Method for fabricating a localize SOI in bulk silicon substrate including changing first trenches formed in the substrate into unclosed empty space by applying heat treatment". United States Patent US 7,507,634 B2, 24 March 2009.

## Figures used in the abstract

Figure 1: Simulation with Moving Mesh.

Figure 2: Simulation with the Level-Set method and no coalescence.

Figure 3: Simulation with the Level-Set method with coalescence.